-

Notifications

You must be signed in to change notification settings - Fork 129

NetFPGA 10G 10G Ethernet Interface Loopback Test

mshahbaz edited this page Jul 16, 2012

·

6 revisions

loopback_test

projects/loopback_test

- NetFPGA-10G Specific cores

- Xilinx AXI Peripheral

- Microblaze Subsystem

- Other

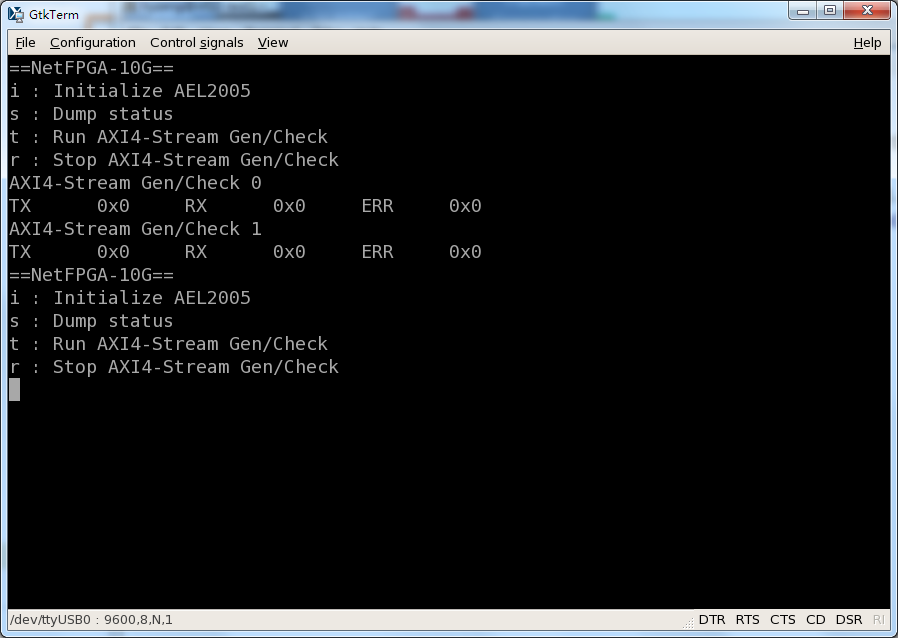

This example project shows the usage of the 10G Ethernet interface on NetFPGA-10G board. Outside the FPGA, the interfaces are paired up using either Direct Attach cable or 10GBASE-R optical fiber. Inside the FPGA, Two packet generator/checkers are connected to two out of the four 10G interfaces while the rest two are looped back together. MicroBlaze subsystem will poll the statistics out of the packet generator/checkers and output them through the UART interface.

- Build the bitfile. Please read the README under projects/loopback_test/ for detailed instructions. This process will take up to an hour. However, you may skip this step if you have a pre-built bitfile available.

- Connect Port 0 to Port 1, and Port 2 and Port 3 on the NetFPGA-10G board using either Direct Attach cable or 10GBASE-R optical fiber.

- Connect UART to the serial port (RS232) on your PC. Open a terminal (PuTTY on Windows or minicom/gtkterm on Linux) and listen to your serial port.

- Download the bitfile to the FPGA and follow the instructions on the terminal (see the screenshot below).