-

Notifications

You must be signed in to change notification settings - Fork 4

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

[SYCL][Graph] Node Profiling #353

Commits on Jan 31, 2024

-

Configuration menu - View commit details

-

Copy full SHA for 292b508 - Browse repository at this point

Copy the full SHA 292b508View commit details -

Configuration menu - View commit details

-

Copy full SHA for 8a98091 - Browse repository at this point

Copy the full SHA 8a98091View commit details -

[InstCombine] Simplify and/or by replacing operands with constants (#…

…77231) This patch tries to simplify `X | Y` by replacing occurrences of `Y` in `X` with 0. Similarly, it tries to simplify `X & Y` by replacing occurrences of `Y` in `X` with -1. Alive2: https://alive2.llvm.org/ce/z/cNjDTR Note: As the current implementation is too conservative in the one-use checks, I cannot remove other existing hard-coded simplifications if they involves more than two instructions (e.g, `A & ~(A ^ B) --> A & B`). Compile-time impact: http://llvm-compile-time-tracker.com/compare.php?from=a085402ef54379758e6c996dbaedfcb92ad222b5&to=9d655c6685865ffce0ad336fed81228f3071bd03&stat=instructions%3Au |stage1-O3|stage1-ReleaseThinLTO|stage1-ReleaseLTO-g|stage1-O0-g|stage2-O3|stage2-O0-g|stage2-clang| |--|--|--|--|--|--|--| |+0.01%|-0.00%|+0.00%|-0.02%|+0.01%|+0.02%|-0.01%| Fixes #76554.

Configuration menu - View commit details

-

Copy full SHA for f2816ff - Browse repository at this point

Copy the full SHA f2816ffView commit details -

[clang][Interp] Add inline descriptor to global variables (#72892)

Some time ago, I did a similar patch for local variables. Initializing global variables can fail as well: ```c++ constexpr int a = 1/0; static_assert(a == 0); ``` ... would succeed in the new interpreter, because we never saved the fact that `a` has not been successfully initialized.

Configuration menu - View commit details

-

Copy full SHA for 5bb99ed - Browse repository at this point

Copy the full SHA 5bb99edView commit details -

[NFC] Update .git-blame-ignore-revs for compiler-rt builtins (#79803)

Configuration menu - View commit details

-

Copy full SHA for 6f35f1d - Browse repository at this point

Copy the full SHA 6f35f1dView commit details -

[NFC] Add compiler-rt:* to .github/new-prs-labeler.yml (#79872)

After this change, all current compiler-rt:* labels on GitHub are covered.

Configuration menu - View commit details

-

Copy full SHA for 9594746 - Browse repository at this point

Copy the full SHA 9594746View commit details -

[clang][dataflow] Extend debug output for

Environment. (#79982)* Print `ReturnLoc`, `ReturnVal`, and `ThisPointeeLoc` if applicable. * For entries in `LocToVal` that correspond to declarations, print the names of the declarations next to them. I've removed the FIXME because all relevant fields are now being dumped. I'm not sure we actually need the capability for the caller to specify which fields to dump, so I've simply deleted this part of the comment. Some examples of the output:

Configuration menu - View commit details

-

Copy full SHA for c83ec84 - Browse repository at this point

Copy the full SHA c83ec84View commit details -

[AMDGPU]: Fix type signatures for wmma intrinsics, NFC (#80087)

Make the wmma intrinsic type signatures to be canonical. We need a type signature as long as the type is not fixed. However, when an argument's type matches a previous argument's type, we do not need the signature for this argument. This patch fixes three general cases: 1. add missing signatures 2. remove signatures for matching arguments 3. reorer the signatures -- return type signature should always appear first

Configuration menu - View commit details

-

Copy full SHA for 3564666 - Browse repository at this point

Copy the full SHA 3564666View commit details -

[clang] static operators should evaluate object argument (reland) (#8…

…0108) This re-applies 30155fc with a fix for clangd. ### Description clang don't evaluate the object argument of `static operator()` and `static operator[]` currently, for example: ```cpp #include <iostream> struct Foo { static int operator()(int x, int y) { std::cout << "Foo::operator()" << std::endl; return x + y; } static int operator[](int x, int y) { std::cout << "Foo::operator[]" << std::endl; return x + y; } }; Foo getFoo() { std::cout << "getFoo()" << std::endl; return {}; } int main() { std::cout << getFoo()(1, 2) << std::endl; std::cout << getFoo()[1, 2] << std::endl; } ``` `getFoo()` is expected to be called, but clang don't call it currently (17.0.6). This PR fixes this issue. Fixes #67976, reland #68485. ### Walkthrough - **clang/lib/Sema/SemaOverload.cpp** - **`Sema::CreateOverloadedArraySubscriptExpr` & `Sema::BuildCallToObjectOfClassType`** Previously clang generate `CallExpr` for static operators, ignoring the object argument. In this PR `CXXOperatorCallExpr` is generated for static operators instead, with the object argument as the first argument. - **`TryObjectArgumentInitialization`** `const` / `volatile` objects are allowed for static methods, so that we can call static operators on them. - **clang/lib/CodeGen/CGExpr.cpp** - **`CodeGenFunction::EmitCall`** CodeGen changes for `CXXOperatorCallExpr` with static operators: emit and ignore the object argument first, then emit the operator call. - **clang/lib/AST/ExprConstant.cpp** - **`ExprEvaluatorBase::handleCallExpr`** Evaluation of static operators in constexpr also need some small changes to work, so that the arguments won't be out of position. - **clang/lib/Sema/SemaChecking.cpp** - **`Sema::CheckFunctionCall`** Code for argument checking also need to be modify, or it will fail the test `clang/test/SemaCXX/overloaded-operator-decl.cpp`. - **clang-tools-extra/clangd/InlayHints.cpp** - **`InlayHintVisitor::VisitCallExpr`** Now that the `CXXOperatorCallExpr` for static operators also have object argument, we should also take care of this situation in clangd. ### Tests - **Added:** - **clang/test/AST/ast-dump-static-operators.cpp** Verify the AST generated for static operators. - **clang/test/SemaCXX/cxx2b-static-operator.cpp** Static operators should be able to be called on const / volatile objects. - **Modified:** - **clang/test/CodeGenCXX/cxx2b-static-call-operator.cpp** - **clang/test/CodeGenCXX/cxx2b-static-subscript-operator.cpp** Matching the new CodeGen. ### Documentation - **clang/docs/ReleaseNotes.rst** Update release notes. --------- Co-authored-by: Shafik Yaghmour <shafik@users.noreply.github.com> Co-authored-by: cor3ntin <corentinjabot@gmail.com> Co-authored-by: Aaron Ballman <aaron@aaronballman.com>

Configuration menu - View commit details

-

Copy full SHA for ee01a2c - Browse repository at this point

Copy the full SHA ee01a2cView commit details -

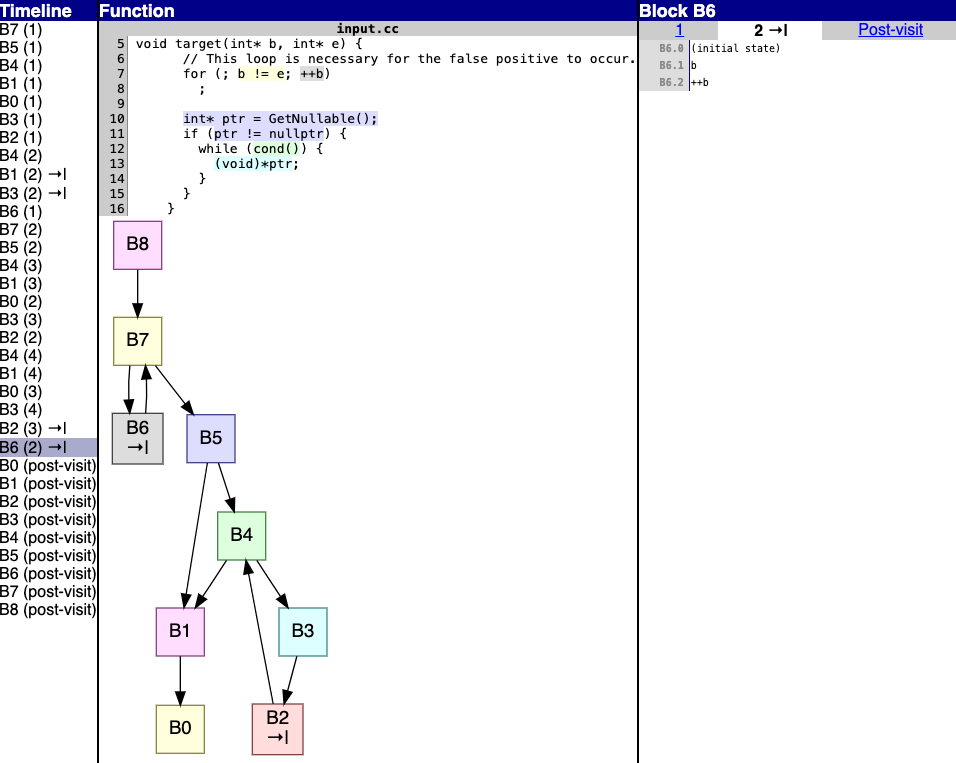

[clang][dataflow] In the CFG visualization, mark converged blocks. (#…

…79999) Here's an example of the output:

Configuration menu - View commit details

-

Copy full SHA for 82324bc - Browse repository at this point

Copy the full SHA 82324bcView commit details -

[ADT] Use a constexpr version of llvm::bit_ceil (NFC) (#79709)

This patch replaces the template trick with a constexpr function that is more readable. Once C++20 is available in our code base, we can remove the constexpr function in favor of std::bit_ceil.

Configuration menu - View commit details

-

Copy full SHA for b49b3dd - Browse repository at this point

Copy the full SHA b49b3ddView commit details -

[SYCL][Fusion] Enable fusion of rounded-range kernels (intel#12492)

Enable, test, and document the support for fusing rounded range kernels. This mostly worked already – we just have to query the original kernel's global size, and use that to compute the private memory size used for internalization. --------- Signed-off-by: Julian Oppermann <julian.oppermann@codeplay.com>

Configuration menu - View commit details

-

Copy full SHA for a3e2315 - Browse repository at this point

Copy the full SHA a3e2315View commit details -

[InstCombine] Fold select with signbit idiom into fabs (#76342)

This patch folds: ``` ((bitcast X to int) <s 0 ? -X : X) -> fabs(X) ((bitcast X to int) >s -1 ? X : -X) -> fabs(X) ((bitcast X to int) <s 0 ? X : -X) -> -fabs(X) ((bitcast X to int) >s -1 ? -X : X) -> -fabs(X) ``` Alive2: https://alive2.llvm.org/ce/z/rGepow

Configuration menu - View commit details

-

Copy full SHA for f292f90 - Browse repository at this point

Copy the full SHA f292f90View commit details -

[SYCL] [NATIVECPU] Update OneAPI Construction Kit tag (intel#12543)

Updates the commit tag for the OCK.

Configuration menu - View commit details

-

Copy full SHA for 565490d - Browse repository at this point

Copy the full SHA 565490dView commit details -

[SYCL][Joint matrix tests] Fix test execution env setting for two tes…

…ts (intel#12529) This will make the two tests run in the presence of either CPU OR GPU and not requiring both to be present to run.

Configuration menu - View commit details

-

Copy full SHA for 6ec040e - Browse repository at this point

Copy the full SHA 6ec040eView commit details -

[NFC] [clang-repl] Fix test failures due to incosistent target settings

See llvm/llvm-project#79261 for details. It shows that clang-repl uses a different target triple with clang so that it may be problematic if the calng-repl reads the generated BMI from clang in a different target triple. While the underlying issue is not easy to fix, this patch tries to make this test green to not bother developers.

Configuration menu - View commit details

-

Copy full SHA for d71831a - Browse repository at this point

Copy the full SHA d71831aView commit details -

[SYCL][Fusion] Improve error messages on incompatible ND-ranges (inte…

…l#12524) Show detailed error messages when users try to fuse kernels with incompatible ND-ranges, showing different errors for each different scenario. Also combine the validation and fusion logic to reduce the number of ND-ranges list traversals. --------- Signed-off-by: Victor Perez <victor.perez@codeplay.com>

Configuration menu - View commit details

-

Copy full SHA for 7d492f8 - Browse repository at this point

Copy the full SHA 7d492f8View commit details -

[RISCV][Isel] Remove redundant vmerge for the scalable vwadd(u).wv (#…

…80079) Similar to #78403, but for scalable `vwadd(u).wv`, given that #76785 is recommited. ### Code ``` define <vscale x 8 x i64> @vwadd_wv_mask_v8i32(<vscale x 8 x i32> %x, <vscale x 8 x i64> %y) { %mask = icmp slt <vscale x 8 x i32> %x, shufflevector (<vscale x 8 x i32> insertelement (<vscale x 8 x i32> poison, i32 42, i64 0), <vscale x 8 x i32> poison, <vscale x 8 x i32> zeroinitializer) %a = select <vscale x 8 x i1> %mask, <vscale x 8 x i32> %x, <vscale x 8 x i32> zeroinitializer %sa = sext <vscale x 8 x i32> %a to <vscale x 8 x i64> %ret = add <vscale x 8 x i64> %sa, %y ret <vscale x 8 x i64> %ret } ``` ### Before this patch [Compiler Explorer](https://godbolt.org/z/xsoa5xPrd) ``` vwadd_wv_mask_v8i32: li a0, 42 vsetvli a1, zero, e32, m4, ta, ma vmslt.vx v0, v8, a0 vmv.v.i v12, 0 vmerge.vvm v24, v12, v8, v0 vwadd.wv v8, v16, v24 ret ``` ### After this patch ``` vwadd_wv_mask_v8i32: li a0, 42 vsetvli a1, zero, e32, m4, ta, ma vmslt.vx v0, v8, a0 vsetvli zero, zero, e32, m4, tu, mu vwadd.wv v16, v16, v8, v0.t vmv8r.v v8, v16 ret ```Configuration menu - View commit details

-

Copy full SHA for dc5dca1 - Browse repository at this point

Copy the full SHA dc5dca1View commit details -

[mlir][memref]

memref.subview: Verify result strides (#79865)The `memref.subview` verifier currently checks result shape, element type, memory space and offset of the result type. However, the strides of the result type are currently not verified. This commit adds verification of result strides for non-rank reducing ops and fixes invalid IR in test cases. Verification of result strides for ops with rank reductions is more complex (and there could be multiple possible result types). That is left for a separate commit. Also refactor the implementation a bit: * If `computeMemRefRankReductionMask` could not compute the dropped dimensions, there must be something wrong with the op. Return `FailureOr` instead of `std::optional`. * `isRankReducedMemRefType` did much more than just checking whether the op has rank reductions or not. Inline the implementation into the verifier and add better comments. * `produceSubViewErrorMsg` does not have to be templatized.

Configuration menu - View commit details

-

Copy full SHA for db49319 - Browse repository at this point

Copy the full SHA db49319View commit details -

[CodeGen] Don't include aliases in RegisterClassInfo::IgnoreCSRForAll…

…ocOrder (#80015) Previously we called ignoreCSRForAllocationOrder on every alias of every CSR which was expensive on targets like AMDGPU which define a very large number of overlapping register tuples. On such targets it is simpler and faster to call ignoreCSRForAllocationOrder once for every physical register. Differential Revision: https://reviews.llvm.org/D146735

Configuration menu - View commit details

-

Copy full SHA for f852503 - Browse repository at this point

Copy the full SHA f852503View commit details -

Revert "[mlir][memref]

memref.subview: Verify result strides" (#80116)Reverts llvm/llvm-project#79865 I think there is a bug in the stride computation in `SubViewOp::inferResultType`. (Was already there before this change.) Reverting this commit for now and updating the original pull request with a fix and more test cases.

Configuration menu - View commit details

-

Copy full SHA for 96c907d - Browse repository at this point

Copy the full SHA 96c907dView commit details -

Turn on LLVM_USE_SPLIT_DWARF by default for Linux Debug build (intel#…

…12527) split-dwarf feature can help reducing compile time and build footprint See examples from: https://www.productive-cpp.com/improving-cpp-builds-with-split-dwarf/ Locally measured size reduction using debug build shows around 20% reduction for static linked build. Footprint reduction using after compile.py: 48G -> 37G (23%) after check-all: 170G -> 140G (18%) Debugability should not be affected. Should help with compile time, especially incremental build as well. -gsplit-dwarf not yet supported on windows, so not turn it on for now.

Configuration menu - View commit details

-

Copy full SHA for 2f20e37 - Browse repository at this point

Copy the full SHA 2f20e37View commit details -

[SYCL] Ensure that RTDeviceBinaryImage instances have a unique image …

…ID (intel#12526) **Problem:** Currently, the image id of an RTDeviceBinaryImage instance is simply the pointer value of the underlying pi_device_binary (in [getImageID(](https://github.com/intel/llvm/blob/sycl/sycl/source/detail/device_binary_image.hpp#L221))). However, consider the following scenario: 1) We create a device image 2) Put into cache 3) Destroy the image (when it goes out of scope) 4) Create another image that _happens to be created at the same memory address_ (thus having same image ID) This causes two instances of RTDeviceBinaryImage to share the same image id, which ends up causing a collision in the KernelProgramCache. **Solution (Proposed in this PR)** Have a counter in RTDeviceBinaryImage that increments upon instantiation of this class. The counter value is added to the image id to ensure that no two instances have the same ID. **Alternative Solutions** 1. Remove the entry from the KernelProgramCache when the image is destroyed. This solution would require more work as the KernelProgramCache, currently, [does not support arbitrary element-wise eviction](https://github.com/intel/llvm/blob/sycl/sycl/doc/design/KernelProgramCache.md#in-memory-cache-eviction) (eviction follows a LRU strategy when cache size exceeds the threshold). Moreover, I expect this to have additional performance overhead of having to lock the cache and evicting. The proposed solution is much more simpler.

Configuration menu - View commit details

-

Copy full SHA for 04ff5b8 - Browse repository at this point

Copy the full SHA 04ff5b8View commit details -

[clang][Interp] Support arbitrary precision constants (#79747)

Add (de)serialization support for them, like we do for Floating values.

Configuration menu - View commit details

-

Copy full SHA for 64a849a - Browse repository at this point

Copy the full SHA 64a849aView commit details -

Add support of param type for transform.structured.tile_using_forall …

…(#72097) Make transform.structured.tile_using_forall be able to take param type tile sizes. Examples: ``` %tile_sizes = transform.param.constant 16 : i64 -> !transform.param<i64> transform.structured.tile_using_forall %matmul tile_sizes [%tile_sizes : !transform.param<i64>, 32] ( mapping = [#gpu.block<x>, #gpu.block<y>] ) : (!transform.any_op) -> (!transform.any_op, !transform.any_op) ``` ``` %c10 = transform.param.constant 10 : i64 -> !transform.any_param %c20 = transform.param.constant 20 : i64 -> !transform.any_param %tile_sizes = transform.merge_handles %c10, %c20 : !transform.any_param transform.structured.tile_using_forall %matmul tile_sizes *(%tile_sizes : !transform.any_param) ( mapping = [#gpu.block<x>, #gpu.block<y>] ) : (!transform.any_op) -> (!transform.any_op, !transform.any_op) ```

Configuration menu - View commit details

-

Copy full SHA for d439f36 - Browse repository at this point

Copy the full SHA d439f36View commit details -

[SME] Stop RA from coalescing COPY instructions that transcend beyond…

… smstart/smstop. (#78294) This patch introduces a 'COALESCER_BARRIER' which is a pseudo node that expands to a 'nop', but which stops the register allocator from coalescing a COPY node when its use/def crosses a SMSTART or SMSTOP instruction. For example: %0:fpr64 = COPY killed $d0 undef %2.dsub:zpr = COPY %0 // <- Do not coalesce this COPY ADJCALLSTACKDOWN 0, 0 MSRpstatesvcrImm1 1, 0, csr_aarch64_smstartstop, implicit-def dead $d0 $d0 = COPY killed %0 BL @use_f64, csr_aarch64_aapcs If the COPY would be coalesced, that would lead to: $d0 = COPY killed %0 being replaced by: $d0 = COPY killed %2.dsub which means the whole ZPR reg would be live upto the call, causing the MSRpstatesvcrImm1 (smstop) to spill/reload the ZPR register: str q0, [sp] // 16-byte Folded Spill smstop sm ldr z0, [sp] // 16-byte Folded Reload bl use_f64 which would be incorrect for two reasons: 1. The program may load more data than it has allocated. 2. If there are other SVE objects on the stack, the compiler might use the 'mul vl' addressing modes to access the spill location. By disabling the coalescing, we get the desired results: str d0, [sp, #8] // 8-byte Folded Spill smstop sm ldr d0, [sp, #8] // 8-byte Folded Reload bl use_f64Configuration menu - View commit details

-

Copy full SHA for dd73666 - Browse repository at this point

Copy the full SHA dd73666View commit details -

[RISCV][MC] Add MC layer support for the experimental zabha extension…

… (#80005) This patch implements the zabha (Byte and Halfword Atomic Memory Operations) v1.0-rc1 extension. See also https://github.com/riscv/riscv-zabha/blob/v1.0-rc1/zabha.adoc.

Configuration menu - View commit details

-

Copy full SHA for 89f87c3 - Browse repository at this point

Copy the full SHA 89f87c3View commit details -

[mlir][transform] Add elementwise criteria to

match.structured.body…… (#79626) As far as I am aware, there is no simple way to match on elementwise ops. I propose to add an `elementwise` criteria to the `match.structured.body` op. Although my only hesitation is that elementwise is not only determined by the body, but also the indexing maps. So if others find this too awkward, I can implement a separate match op instead.

Configuration menu - View commit details

-

Copy full SHA for 488f88b - Browse repository at this point

Copy the full SHA 488f88bView commit details -

[mlir][ArmSME] Support 2-way widening outer products (#78975)

This patch introduces support for 2-way widening outer products. This enables the fusion of 2 'arm_sme.outerproduct' operations that are chained via the accumulator into a 2-way widening outer product operation. Changes: - Add 'llvm.aarch64.sme.[us]mop[as].za32' intrinsics for 2-way variants. These map to instruction variants added in SME2 and use different intrinsics. Intrinsics are already implemented for widening variants from SME1. - Adds the following operations: - fmopa_2way, fmops_2way - smopa_2way, smops_2way - umopa_2way, umops_2way - Implements conversions for the above ops to intrinsics in ArmSMEToLLVM. - Adds a pass 'arm-sme-outer-product-fusion' that fuses 'arm_sme.outerproduct' operations. For a detailed description of these operations see the 'arm_sme.fmopa_2way' description. The reason for introducing many operations rather than one is the signed/unsigned variants can't be distinguished with types (e.g., ui16, si16) since 'arith.extui' and 'arith.extsi' only support signless integers. A single operation would require this information and an attribute (for example) for the sign doesn't feel right if floating-point types are also supported where this wouldn't apply. Furthermore, the SME FP8 extensions (FEAT_SME_F8F16, FEAT_SME_F8F32) introduce FMOPA 2-way (FP8 to FP16) and 4-way (FP8 to FP32) variants but no subtract variant. Whilst these are not supported in this patch, it felt simpler to have separate ops for add/subtract given this.

Configuration menu - View commit details

-

Copy full SHA for 95ef8e3 - Browse repository at this point

Copy the full SHA 95ef8e3View commit details -

[mlir][vector] Disable transpose -> shuffle lowering for scalable vec…

…tors (#79979) vector.shuffle is not supported for scalable vectors (outside of splats)

Configuration menu - View commit details

-

Copy full SHA for 88610b7 - Browse repository at this point

Copy the full SHA 88610b7View commit details -

[mlir][memref]

memref.subview: Verify result stridesThe `memref.subview` verifier currently checks result shape, element type, memory space and offset of the result type. However, the strides of the result type are currently not verified. This commit adds verification of result strides for non-rank reducing ops and fixes invalid IR in test cases. Verification of result strides for ops with rank reductions is more complex (and there could be multiple possible result types). That is left for a separate commit. Also refactor the implementation a bit: * If `computeMemRefRankReductionMask` could not compute the dropped dimensions, there must be something wrong with the op. Return `FailureOr` instead of `std::optional`. * `isRankReducedMemRefType` did much more than just checking whether the op has rank reductions or not. Inline the implementation into the verifier and add better comments. * `produceSubViewErrorMsg` does not have to be templatized. * Fix comment and add additional assert to `ExpandStridedMetadata.cpp`, to make sure that the memref.subview verifier is in sync with the memref.subview -> memref.reinterpret_cast lowering. Note: This change is identical to #79865, but with a fixed comment and an additional assert in `ExpandStridedMetadata.cpp`. (I reverted #79865 in #80116, but the implementation was actually correct, just the comment in `ExpandStridedMetadata.cpp` was confusing.)

Configuration menu - View commit details

-

Copy full SHA for ce7cc72 - Browse repository at this point

Copy the full SHA ce7cc72View commit details -

[SYCL][COMPAT] Force device function to be inlined (intel#12550)

Due to the way the inliner works, the launched function may become very large and go above the inline threshold. This results with a short kernel which only call one function. The patch adds an always_inline on the call site to force the user function to be inline in the SYCL kernel to reduce overhead. Signed-off-by: Victor Lomuller <victor@codeplay.com>

Configuration menu - View commit details

-

Copy full SHA for e121c88 - Browse repository at this point

Copy the full SHA e121c88View commit details -

Merge from 'main' to 'sycl-web' (46 commits)

CONFLICT (content): Merge conflict in clang/lib/Basic/Targets/NVPTX.cpp CONFLICT (content): Merge conflict in clang/test/Driver/cuda-cross-compiling.c

Configuration menu - View commit details

-

Copy full SHA for 9bf5d5c - Browse repository at this point

Copy the full SHA 9bf5d5cView commit details -

Configuration menu - View commit details

-

Copy full SHA for db1fbd6 - Browse repository at this point

Copy the full SHA db1fbd6View commit details -

[GitHub][workflows] Add buildbot information comment to first merged …

…PR from a new contributor (#78292) This change adds a comment to the first PR from a new contributor that is merged, which tells them what to expect post merge from the build bots. How they will be notified, where to ask questions, that you're more likely to be reverted than in other projects, etc. The information overlaps with, and links to https://llvm.org/docs/MyFirstTypoFix.html#myfirsttypofix-issues-after-landing-your-pr. So that users who simply read the email are still aware, and know where to follow up if they do get reports. To do this, I have added a hidden HTML comment to the new contributor greeting comment. This workflow will look for that to tell if the author of the PR was a new contributor at the time they opened the merge. It has to be done this way because as soon as the PR is merged, they are by GitHub's definition no longer a new contributor and I suspect that their author association will be "contributor" instead. I cannot 100% confirm that without a whole lot of effort and probably breaking GitHub's terms of service, but it's fairly cheap to work around anyway. It seems rare / almost impossible to reopen a PR in llvm at least, but in case it does happen the buildbot info comment has its own hidden HTML comment. If we find this we will not post another copy of the same information.

Configuration menu - View commit details

-

Copy full SHA for 44ba4c7 - Browse repository at this point

Copy the full SHA 44ba4c7View commit details -

Configuration menu - View commit details

-

Copy full SHA for 24a8041 - Browse repository at this point

Copy the full SHA 24a8041View commit details -

[BDCE] Fix clearing of poison-generating flags

If the demanded bits of an instruction are full, we don't have to recurse to its users, but we may still have to clear flags on the instruction itself. Fixes llvm/llvm-project#80113.

Configuration menu - View commit details

-

Copy full SHA for b210cbb - Browse repository at this point

Copy the full SHA b210cbbView commit details -

[mlir][IR] Add

RewriterBase::moveBlockBeforeand fix bug in `moveOp……Before` (#79579) This commit adds a new method to the rewriter API: `moveBlockBefore`. This op is utilized by `inlineRegionBefore` and covered by dialect conversion test cases. Also fixes a bug in `moveOpBefore`, where the previous op location was not passed correctly. Adds a test case to `test-strict-pattern-driver.mlir`.

Configuration menu - View commit details

-

Copy full SHA for da784a2 - Browse repository at this point

Copy the full SHA da784a2View commit details -

Revert "[CodeGen] Don't include aliases in RegisterClassInfo::IgnoreC…

…SRForAllocOrder (#80015)" This reverts commit f852503. It was supposed to speed things up but llvm-compile-time-tracker.com showed a slight slow down.

Configuration menu - View commit details

-

Copy full SHA for 942cc9a - Browse repository at this point

Copy the full SHA 942cc9aView commit details -

[ValueTracking] Merge

cannotBeOrderedLessThanZeroImplinto `compute……KnownFPClass` (#76360) This patch merges the logic of `cannotBeOrderedLessThanZeroImpl` into `computeKnownFPClass` to improve the signbit inference. --------- Co-authored-by: Matt Arsenault <arsenm2@gmail.com>

Configuration menu - View commit details

-

Copy full SHA for 50e80e0 - Browse repository at this point

Copy the full SHA 50e80e0View commit details -

[AMDGPU] Stop combining arbitrary offsets into PAL relocs (#80034)

PAL uses ELF REL (not RELA) relocations which can only store a 32-bit addend in the instruction, even for reloc types like R_AMDGPU_ABS32_HI which require the upper 32 bits of a 64-bit address calculation to be correct. This means that it is not safe to fold an arbitrary offset into a GlobalAddressSDNode, so stop doing that. In practice this is mostly a problem for small negative offsets which do not work as expected because PAL treats the 32-bit addend as unsigned.

Configuration menu - View commit details

-

Copy full SHA for c2c650f - Browse repository at this point

Copy the full SHA c2c650fView commit details -

[clang][AMDGPU] Remove trialing whitespace in doc

Added by f2a78e6. Wouldn't normally bother but it's showing up in some CI checks, just want to reduce the noise.

Configuration menu - View commit details

-

Copy full SHA for 0217d2e - Browse repository at this point

Copy the full SHA 0217d2eView commit details -

[SYCL][Bindless] Unique sampler addressing modes per dimension (intel…

…#12109) Add the ability to specify unique addressing modes per dimension to the bindless_image_sampler Corresponding CUDA adapter UR PR: oneapi-src/unified-runtime#1168 --------- Co-authored-by: Kenneth Benzie (Benie) <k.benzie83@gmail.com>

Configuration menu - View commit details

-

Copy full SHA for b897152 - Browse repository at this point

Copy the full SHA b897152View commit details -

Configuration menu - View commit details

-

Copy full SHA for fbbc822 - Browse repository at this point

Copy the full SHA fbbc822View commit details -

Configuration menu - View commit details

-

Copy full SHA for 7ff2327 - Browse repository at this point

Copy the full SHA 7ff2327View commit details -

[mlir] Fix debug output for passes that modify top-level operation. (…

…#80022) Make it so that when the top-level (root) operation itself is being modified, it is also used as the root for debug output in PatternApplicator. Fix #80021

Configuration menu - View commit details

-

Copy full SHA for 78e0cca - Browse repository at this point

Copy the full SHA 78e0ccaView commit details -

[mlir][EmitC] Add

verbatimop (#79584)The `verbatim` operation produces no results and the value is emitted as is followed by a line break ('\n' character) during translation. Note: Use with caution. This operation can have arbitrary effects on the semantics of the emitted code. Use semantically more meaningful operations whenever possible. Additionally this op is *NOT* intended to be used to inject large snippets of code. This operation can be used in situations where a more suitable operation is not yet implemented in the dialect or where preprocessor directives interfere with the structure of the code. Co-authored-by: Marius Brehler <marius.brehler@iml.fraunhofer.de>Configuration menu - View commit details

-

Copy full SHA for e624648 - Browse repository at this point

Copy the full SHA e624648View commit details -

[SPIR-V] Improve how lowering of formal arguments in SPIR-V Backend i…

…nterprets a value of 'kernel_arg_type' (#78730) The goal of this PR is to tolerate differences between description of formal arguments by function metadata (represented by "kernel_arg_type") and LLVM actual parameter types. A compiler may use "kernel_arg_type" of function metadata fields to encode detailed type information, whereas LLVM IR may utilize for an actual parameter a more general type, in particular, opaque pointer type. This PR proposes to resolve this by a fallback to LLVM actual parameter types during the lowering of formal function arguments in cases when the type can't be created by string content of "kernel_arg_type", i.e., when "kernel_arg_type" contains a type unknown for the SPIR-V Backend. An example of the issue manifestation is https://github.com/KhronosGroup/SPIRV-LLVM-Translator/blob/main/test/transcoding/KernelArgTypeInOpString.ll, where a compiler generates for the following kernel function detailed `kernel_arg_type` info in a form of `!{!"image_kernel_data*", !"myInt", !"struct struct_name*"}`, and in LLVM IR same arguments are referred to as `@foo(ptr addrspace(1) %in, i32 %out, ptr addrspace(1) %outData)`. Both definitions are correct, and the resulting LLVM IR is correct, but lowering stage of SPIR-V Backend fails to generate SPIR-V type. ``` typedef int myInt; typedef struct { int width; int height; } image_kernel_data; struct struct_name { int i; int y; }; void kernel foo(__global image_kernel_data* in, __global struct struct_name *outData, myInt out) {} ``` ``` define spir_kernel void @foo(ptr addrspace(1) %in, i32 %out, ptr addrspace(1) %outData) ... !kernel_arg_type !7 ... { entry: ret void } ... !7 = !{!"image_kernel_data*", !"myInt", !"struct struct_name*"} ``` The PR changes a contract of `SPIRVType *getArgSPIRVType(...)` in a way that it may return `nullptr` to signal that the metadata string content is not recognized, so corresponding comments are added and a couple of checks for `nullptr` are inserted where appropriate.

Configuration menu - View commit details

-

Copy full SHA for 5a07774 - Browse repository at this point

Copy the full SHA 5a07774View commit details -

[X86] i256-add - replace i386 triple X32 check prefixes with X86 and …

…add gnux32 triple tests

Configuration menu - View commit details

-

Copy full SHA for 53b9d47 - Browse repository at this point

Copy the full SHA 53b9d47View commit details -

[X86] mmx-arith.ll - replace X32 check prefixes with X86 + strip cfi …

…noise We try to only use X32 for gnux32 triple tests.

Configuration menu - View commit details

-

Copy full SHA for 8d450b4 - Browse repository at this point

Copy the full SHA 8d450b4View commit details -

[X86] v4f32-immediate.ll - replace X32 check prefixes with X86

We try to only use X32 for gnux32 triple tests.

Configuration menu - View commit details

-

Copy full SHA for 00a6817 - Browse repository at this point

Copy the full SHA 00a6817View commit details -

[X86] v2f32.ll - replace X32 check prefixes with X86 (and add common …

…CHECK prefix) We try to only use X32 for gnux32 triple tests.

Configuration menu - View commit details

-

Copy full SHA for 929503e - Browse repository at this point

Copy the full SHA 929503eView commit details -

Configuration menu - View commit details

-

Copy full SHA for 3f5fcb5 - Browse repository at this point

Copy the full SHA 3f5fcb5View commit details -

[OpenMPIRBuilder] Do not call host runtime for GPU teams codegen (#79…

…984) Patch ensures that host runtime functions are not called for handling OpenMP teams clause on the device. GPU code for pragma `omp target teams distribute parallel do` will require only one call to OpenMP loop-worksharing GPU runtime. Support for it will be added later. This patch does not include changes required for handling `omp target teams` for the host side.

Configuration menu - View commit details

-

Copy full SHA for b437014 - Browse repository at this point

Copy the full SHA b437014View commit details -

[BDCE] Also drop poison-generating metadata

The comment was incorrect: !range also applies to calls, and we do need to drop it in some cases.

Configuration menu - View commit details

-

Copy full SHA for cb6240d - Browse repository at this point

Copy the full SHA cb6240dView commit details -

[AsmParser] Add missing globals declarations in incomplete IR mode (#…

…79855) If `-allow-incomplete-ir` is enabled, automatically insert declarations for missing globals. If a global is only used in calls with the same function type, insert a function declaration with that type. Otherwise, insert a dummy i8 global. The fallback case could be extended with various heuristics (e.g. we could look at load/store types), but I've chosen to keep it simple for now, because I'm unsure to what degree this would really useful without more experience. I expect that in most cases the declaration type doesn't really matter (note that the type of an external global specifies a *minimum* size only, not a precise size). This is a followup to llvm/llvm-project#78421.

Configuration menu - View commit details

-

Copy full SHA for 5cc87b4 - Browse repository at this point

Copy the full SHA 5cc87b4View commit details -

[OpenMP] atomic compare weak : Parser & AST support (#79475)

This is a support for " #pragma omp atomic compare weak". It has Parser & AST support for now. --------- Authored-by: Sunil Kuravinakop <kuravina@pe28vega.us.cray.com>

Configuration menu - View commit details

-

Copy full SHA for a74e9ce - Browse repository at this point

Copy the full SHA a74e9ceView commit details -

[AArch64][SME] Fix inlining bug introduced in #78703 (#79994)

Calling a `__arm_locally_streaming` function from a function that is not a streaming-SVE function would lead to incorrect inlining. The issue didn't surface because the tests were not testing what they were supposed to test.

Configuration menu - View commit details

-

Copy full SHA for 3abf55a - Browse repository at this point

Copy the full SHA 3abf55aView commit details -

[llvm][InstCombine] bitcast bfloat half castpair bug (#79832)

Miscompilation arises due to instruction combining of cast pairs of the type `bitcast bfloat to half` + `<FPOp> bfloat to half` or `bitcast half to bfloat` + `<FPOp half to bfloat`. For example `bitcast bfloat to half`+`fpext half to double` or `bitcast bfloat to half`+`fpext bfloat to double` respectively reduce to `fpext bfloat to double` and `fpext half to double`. This is an incorrect conversion as it assumes the representation of `bfloat` and `half` are equivalent due to having the same width. As a consequence miscompilation arises. Fixes #61984

Configuration menu - View commit details

-

Copy full SHA for d309261 - Browse repository at this point

Copy the full SHA d309261View commit details -

[llvm-rc] Support ARM64EC resource generation (#78908)

This is already supported in llvm-cvtres, so only a small change is needed.

Configuration menu - View commit details

-

Copy full SHA for d55d72e - Browse repository at this point

Copy the full SHA d55d72eView commit details -

Configuration menu - View commit details

-

Copy full SHA for d74619a - Browse repository at this point

Copy the full SHA d74619aView commit details -

[mlir][ArmSME] Add initial SME vector legalization pass (#79152)

This adds a new pass (`-arm-sme-vector-legalization`) which legalizes vector operations so that they can be lowered to ArmSME. This initial patch adds decomposition for `vector.outerproduct`, `vector.transfer_read`, and `vector.transfer_write` when they operate on vector types larger than a single SME tile. For example, a [8]x[8]xf32 outer product would be decomposed into four [4]x[4]xf32 outer products, which could then be lowered to ArmSME. These three ops have been picked as supporting them alone allows lowering matmuls that use all ZA accumulators to ArmSME. For it to be possible to legalize a vector type it has to be a multiple of an SME tile size, but other than that any shape can be used. E.g. `vector<[8]x[8]xf32>`, `vector<[4]x[16]xf32>`, `vector<[16]x[4]xf32>` can all be lowered to four `vector<[4]x[4]xf32>` operations. In future, this pass will be extended with more SME-specific rewrites to legalize unrolling the reduction dimension of matmuls (which is not type-decomposition), which is why the pass has quite a general name.

Configuration menu - View commit details

-

Copy full SHA for 042800a - Browse repository at this point

Copy the full SHA 042800aView commit details -

[DAG] AddNodeIDCustom - call ShuffleVectorSDNode::getMask once instea…

…d of repeated getMaskElt calls. Use a simpler for-range loop to append all shuffle mask elements

Configuration menu - View commit details

-

Copy full SHA for 912cdd2 - Browse repository at this point

Copy the full SHA 912cdd2View commit details -

[X86] insertps-from-constantpool.ll - replace X32 check prefixes with…

… X86 and expose address math We try to only use X32 for gnux32 triple tests. Use no_x86_scrub_mem_shuffle so the test shows updated shuffle intermediate and the +4 offset into the constant pool vector entry

Configuration menu - View commit details

-

Copy full SHA for a82ca1c - Browse repository at this point

Copy the full SHA a82ca1cView commit details -

[X86] divrem.ll - replace X32 check prefixes with X86

We try to only use X32 for gnux32 triple tests.

Configuration menu - View commit details

-

Copy full SHA for e4af212 - Browse repository at this point

Copy the full SHA e4af212View commit details -

[X86] divide-by-constant.ll - replace X32 check prefixes with X86

We try to only use X32 for gnux32 triple tests.

Configuration menu - View commit details

-

Copy full SHA for ed11f25 - Browse repository at this point

Copy the full SHA ed11f25View commit details -

[X86] fold-vector-sext - replace X32 check prefixes with X86

We try to only use X32 for gnux32 triple tests.

Configuration menu - View commit details

-

Copy full SHA for 824d073 - Browse repository at this point

Copy the full SHA 824d073View commit details -

[X86] cfguard - replace X32 check prefixes with X86

We try to only use X32 for gnux32 triple tests.

Configuration menu - View commit details

-

Copy full SHA for 1d8c8f1 - Browse repository at this point

Copy the full SHA 1d8c8f1View commit details -

[X86] divrem8_ext.ll - replace X32 check prefixes with X86

We try to only use X32 for gnux32 triple tests.

Configuration menu - View commit details

-

Copy full SHA for 648eb7c - Browse repository at this point

Copy the full SHA 648eb7cView commit details -

[SYCL][Fusion] Silence warning (intel#12555)

Silence unused variable warning which tripped post-commit checks for intel#12492. Signed-off-by: Julian Oppermann <julian.oppermann@codeplay.com>

Configuration menu - View commit details

-

Copy full SHA for b8f9c8b - Browse repository at this point

Copy the full SHA b8f9c8bView commit details -

[AArch64] Convert concat(uhadd(a,b), uhadd(c,d)) to uhadd(concat(a,c)…

…, concat(b,d)) (#79464) We can convert concat(v4i16 uhadd(a,b), v4i16 uhadd(c,d)) to v8i16 uhadd(concat(a,c), concat(b,d)), which can lead to further simplifications.

Configuration menu - View commit details

-

Copy full SHA for cf828ae - Browse repository at this point

Copy the full SHA cf828aeView commit details -

[X86][CodeGen] Set isReMaterializable = 1 for AVX broadcast load

Broadcast of a single float should not be any slower than loading 32B using vmovaps. So remat it can help reduce register spill when there is big register pressure.

Configuration menu - View commit details

-

Copy full SHA for e3c9327 - Browse repository at this point

Copy the full SHA e3c9327View commit details -

[AMDGPU][GFX12] Add tests for unsupported builtins (#78729)

__builtin_amdgcn_mfma* and __builtin_amdgcn_smfmac*

Configuration menu - View commit details

-

Copy full SHA for f96e85b - Browse repository at this point

Copy the full SHA f96e85bView commit details -

[X86][MC] Support encoding/decoding for APX variant LZCNT/TZCNT/POPCN…

…T instructions (#79954) Two variants: promoted legacy, NF (no flags update). The syntax of NF instructions is aligned with GNU binutils. https://sourceware.org/pipermail/binutils/2023-September/129545.html

Configuration menu - View commit details

-

Copy full SHA for d9e875d - Browse repository at this point

Copy the full SHA d9e875dView commit details -

Configuration menu - View commit details

-

Copy full SHA for 817d0cb - Browse repository at this point

Copy the full SHA 817d0cbView commit details -

[VPlan] Preserve original induction order when creating scalar steps.

Update createScalarIVSteps to take an insert point as parameter. This ensures that the inserted scalar steps are in the same order as the recipes they replace (vs in reverse order as currently). This helps to reduce the diff for follow-up changes.

Configuration menu - View commit details

-

Copy full SHA for 9536a62 - Browse repository at this point

Copy the full SHA 9536a62View commit details -

Configuration menu - View commit details

-

Copy full SHA for ab87426 - Browse repository at this point

Copy the full SHA ab87426View commit details -

[mlir][IR] Send missing notifications when inlining a block (#79593)

When a block is inlined into another block, the nested operations are moved into another block and the `notifyOperationInserted` callback should be triggered. This commit adds the missing notifications for: * `RewriterBase::inlineBlockBefore` * `RewriterBase::mergeBlocks`

Configuration menu - View commit details

-

Copy full SHA for c672b34 - Browse repository at this point

Copy the full SHA c672b34View commit details -

Configuration menu - View commit details

-

Copy full SHA for 7e45cfd - Browse repository at this point

Copy the full SHA 7e45cfdView commit details -

[mlir][EmitC] Remove unused attribute from verbatim op (#80142)

The uses of the attribute were removed in code review of #79584, but it's definition was inadvertently kept.

Configuration menu - View commit details

-

Copy full SHA for 121a0ef - Browse repository at this point

Copy the full SHA 121a0efView commit details -

Configuration menu - View commit details

-

Copy full SHA for cec24f0 - Browse repository at this point

Copy the full SHA cec24f0View commit details -

[mlir][IR] Send missing notification when splitting a block (#79597)

When a block is split with `RewriterBase::splitBlock`, a `notifyBlockInserted` notification, followed by `notifyOperationInserted` notifications (for moving over the operations into the new block) should be sent. This commit adds those notifications.

Configuration menu - View commit details

-

Copy full SHA for c2675ba - Browse repository at this point

Copy the full SHA c2675baView commit details -

[ARM][NEON] Add constraint to vld2 Odd/Even Pseudo instructions. (#79…

…287) This ensures the odd/even pseudo instructions are allocated to the same register range. This fixes #71763

Configuration menu - View commit details

-

Copy full SHA for de75e50 - Browse repository at this point

Copy the full SHA de75e50View commit details -

[Driver] Fix erroneous warning for -fcx-limited-range and -fcx-fortra…

…n-rules. (#79821) The options `-fcx-limited-range` and `-fcx-fortran-rules` were added in _https://github.com/llvm/llvm-project/pull/70244_ The code adding the options introduced an erroneous warning. `$ clang -c -fcx-limited-range t1.c` `clang: warning: overriding '' option with '-fcx-limited-range' [-Woverriding-option]` and `$ clang -c -fcx-fortran-rules t1.c` `clang: warning: overriding '' option with '-fcx-fortran-rules' [-Woverriding-option]` The warning doesn't make sense. This patch removes it.

Configuration menu - View commit details

-

Copy full SHA for e538486 - Browse repository at this point

Copy the full SHA e538486View commit details -

[AA][JumpThreading] Don't use DomTree for AA in JumpThreading (#79294)

JumpThreading may perform AA queries while the dominator tree is not up to date, which may result in miscompilations. Fix this by adding a new AAQI option to disable the use of the dominator tree in BasicAA. Fixes llvm/llvm-project#79175.

Configuration menu - View commit details

-

Copy full SHA for 4f32f5d - Browse repository at this point

Copy the full SHA 4f32f5dView commit details -

[mlir] Lower math dialect later in gpu-lower-to-nvvm-pipeline (#78556)

This PR moves lowering of math dialect later in the pipeline. Because math dialect is lowered correctly by `createConvertGpuOpsToNVVMOps` for GPU target, and it needs to run it first.

Configuration menu - View commit details

-

Copy full SHA for 74bf0b1 - Browse repository at this point

Copy the full SHA 74bf0b1View commit details -

[clang] Represent array refs as

TemplateArgument::Declaration(#80050)This returns (probably temporarily) array-referring NTTP behavior to which was prior to #78041 because ~~I'm fed up~~ have no time to fix regressions.

Configuration menu - View commit details

-

Copy full SHA for 9bf4e54 - Browse repository at this point

Copy the full SHA 9bf4e54View commit details -

[MIRPrinter] Don't print space when there is no successor (#80143)

Extra space causes the checks generated by update_mir_test_checks to be unavailable. ``` # NOTE: Assertions have been autogenerated by utils/update_mir_test_checks.py UTC_ARGS: --version 4 # RUN: llc -mtriple=x86_64-- -o - %s -run-pass=none -verify-machineinstrs -simplify-mir | FileCheck %s --- name: foo body: | ; CHECK-LABEL: name: foo ; CHECK: bb.0: ; CHECK-NEXT: successors: ; CHECK-NEXT: {{ $}} ; CHECK-NEXT: {{ $}} ; CHECK-NEXT: bb.1: ; CHECK-NEXT: RET 0, $eax bb.0: successors: bb.1: RET 0, $eax ... ``` The failure log is as follows: ``` llvm/test/CodeGen/MIR/X86/unreachable-block-print.mir:9:16: error: CHECK-NEXT: is on the same line as previous match ; CHECK-NEXT: {{ $}} ^ <stdin>:21:13: note: 'next' match was here successors: ^ <stdin>:21:13: note: previous match ended here successors: ```Configuration menu - View commit details

-

Copy full SHA for b7738e2 - Browse repository at this point

Copy the full SHA b7738e2View commit details -

Revert "[mlir][complex] Prevent underflow in complex.abs (#79786)"

This reverts commit 4effff2. It makes `complex.abs(-1)` return `-1`.

Configuration menu - View commit details

-

Copy full SHA for 70fb96a - Browse repository at this point

Copy the full SHA 70fb96aView commit details -

[SYCL][Fusion] Handle GEPs that were canonicalized to byte offsets (i…

…ntel#12557) Upstream now canonicalizes constant GEPs to represent byte offsets, i.e. using `i8` as source element type. This PR adapts the internalization pass to this change by also remapping GEPs with a constant offset, if that offset is a multiple of the internalized accessor's element size. Signed-off-by: Julian Oppermann <julian.oppermann@codeplay.com>

Configuration menu - View commit details

-

Copy full SHA for 470e378 - Browse repository at this point

Copy the full SHA 470e378View commit details -

[flang] Lower ASYNCHRONOUS variables and IO statements (#80008)

Finish plugging-in ASYNCHRONOUS IO in lowering (GetAsynchronousId was not used yet). Add a runtime implementation for GetAsynchronousId (only the signature was defined). Always return zero since flang runtime "fakes" asynchronous IO (data transfer are always complete, see flang/docs/IORuntimeInternals.md). Update all runtime integer argument and results for IDs to use the AsynchronousId int alias for consistency. In lowering, asynchronous attribute is added on the hlfir.declare of ASYNCHRONOUS variable, but nothing else is done. This is OK given the synchronous aspects of flang IO, but it would be safer to treat these variable as volatile (prevent code motion of related store/loads) since the asynchronous data change can also be done by C defined user procedure (see 18.10.4 Asynchronous communication). Flang lowering anyway does not give enough info for LLVM to do such code motions (the variables that are passed in a call are not given the noescape attribute, so LLVM will assume any later opaque call may modify the related data and would not move load/stores of such variables before/after calls even if it could from a pure Fortran point of view without ASYNCHRONOUS).

Configuration menu - View commit details

-

Copy full SHA for 4679132 - Browse repository at this point

Copy the full SHA 4679132View commit details -

Configuration menu - View commit details

-

Copy full SHA for 47df391 - Browse repository at this point

Copy the full SHA 47df391View commit details -

Revert "[Clang][Sema] fix outline member function template with defau…

…… (#80144) …lt align crash (#78400)" This reverts commit 7b33899. A regression was discovered here: llvm/llvm-project#78400 and the author requested a revert to give time to review.

Configuration menu - View commit details

-

Copy full SHA for 6e6aa44 - Browse repository at this point

Copy the full SHA 6e6aa44View commit details -

[mlir][mesh] Refactoring code organization, tests and docs (#79606)

* Split out `MeshDialect.h` form `MeshOps.h` that defines the dialect class. Reduces include clutter if you care only about the dialect and not the ops. * Expose functions `getMesh` and `collectiveProcessGroupSize`. There functions are useful for outside users of the dialect. * Remove unused code. * Remove examples and tests of mesh.shard attribute in tensor encoding. Per the decision that Spmdization would be performed on sharding annotations and there will be no tensors with sharding specified in the type. For more info see this RFC comment: https://discourse.llvm.org/t/rfc-sharding-framework-design-for-device-mesh/73533/81

Configuration menu - View commit details

-

Copy full SHA for 31fc0a1 - Browse repository at this point

Copy the full SHA 31fc0a1View commit details -

Move the PowerPC/PPCMergeStringPool work to initializer (#77352)

Currently, the `PPCMergeStringPool` merges the global variable after the `AsmPrinter` initializer adds the global variables to its symbol list. This is to move the merging work of `PPCMergeStringPool` to its initializer, just like what GlobalMerge does, to avoid adding merged global variables to the `AsmPrinter` symbol lis.

Configuration menu - View commit details

-

Copy full SHA for 1bab570 - Browse repository at this point

Copy the full SHA 1bab570View commit details -

Fix: CMake Error at cmake/modules/LLVMExternalProjectUtils.cmake:86 (…

…is_msvc_triple) (#80071) Adding quotes around the `${target_triple}` Fix: #78530Configuration menu - View commit details

-

Copy full SHA for c651b2b - Browse repository at this point

Copy the full SHA c651b2bView commit details -

[AST] Add dump() method to TypeLoc (#65484)

The ability to dump AST nodes is important to ad-hoc debugging, and the fact this doesn't work with TypeLoc nodes is an obvious missing feature in e.g. clang-query (`set output dump` simply does nothing). Having TypeLoc::dump(), and enabling DynTypedNode::dump() for such nodes seems like a clear win. It looks like this: ``` int main(int argc, char **argv); FunctionProtoTypeLoc <test.cc:3:1, col:31> 'int (int, char **)' cdecl |-ParmVarDecl 0x30071a8 <col:10, col:14> col:14 argc 'int' | `-BuiltinTypeLoc <col:10> 'int' |-ParmVarDecl 0x3007250 <col:20, col:27> col:27 argv 'char **' | `-PointerTypeLoc <col:20, col:26> 'char **' | `-PointerTypeLoc <col:20, col:25> 'char *' | `-BuiltinTypeLoc <col:20> 'char' `-BuiltinTypeLoc <col:1> 'int' ``` It dumps the lexically nested tree of type locs. This often looks similar to how types are dumped, but unlike types we don't look at desugaring e.g. typedefs, as their underlying types are not lexically spelled here. --- Less clear is exactly when to include these nodes in existing text AST dumps rooted at (TranslationUnit)Decls. These already omit supported nodes sometimes, e.g. NestedNameSpecifiers are often mentioned but not recursively dumped. TypeLocs are a more extreme case: they're ~always more verbose than the current AST dump. So this patch punts on that, TypeLocs are only ever printed recursively as part of a TypeLoc::dump() call. It would also be nice to be able to invoke `clang` to dump a typeloc somehow, like `clang -cc1 -ast-dump`. But I don't know exactly what the best verison of that is, so this patch doesn't do it. --- There are similar (less critical!) nodes: TemplateArgumentLoc etc, these also don't have dump() functions today and are obvious extensions. I suspect that we should add these, and Loc nodes should dump each other (e.g. the ElaboratedTypeLoc `vector<int>::iterator` should dump the NestedNameSpecifierLoc `vector<int>::`, which dumps the TemplateSpecializationTypeLoc `vector<int>::` etc). Maybe this generalizes further to a "full syntactic dump" mode, where even Decls and Stmts would print the TypeLocs they lexically contain. But this may be more complex than useful. --- While here, ConceptReference JSON dumping must be implemented. It's not totally clear to me why this implementation wasn't required before but is now...

Configuration menu - View commit details

-

Copy full SHA for 8d1b1c9 - Browse repository at this point

Copy the full SHA 8d1b1c9View commit details -

[AArch64] MI Scheduler LDP combine follow up (#79003)

This is a follow up of 75d820d, adding more opcodes to the combine target hook enabling more LDP creation. Patch co-authored by Cameron McInally.

Configuration menu - View commit details

-

Copy full SHA for 8841846 - Browse repository at this point

Copy the full SHA 8841846View commit details -

Add a release note for TypeLoc::dump() support; NFC

This amends 8d1b1c9 which added the functionality the release note refers to.

Configuration menu - View commit details

-

Copy full SHA for e33dc6b - Browse repository at this point

Copy the full SHA e33dc6bView commit details -

[AArch64] Use add_and_or_is_add for CSINC (#79552)

Adds or add-like-or's of 1 can both be turned into csinc, which can help fold more instructions into a csinc.

Configuration menu - View commit details

-

Copy full SHA for 5d7d89d - Browse repository at this point

Copy the full SHA 5d7d89dView commit details -

[clang][Interp] Handle casts between complex types (#79269)

Just handle this like two primtive casts.

Configuration menu - View commit details

-

Copy full SHA for 32c0048 - Browse repository at this point

Copy the full SHA 32c0048View commit details -

[clang][Interp] Remove wrong * operator

classifyComplexElementType used to return a std::optional, seems like this was left in a PR and not re-tested. This broke build bots, e.g. https://lab.llvm.org/buildbot/#/builders/68/builds/67930

Configuration menu - View commit details

-

Copy full SHA for dfd5a64 - Browse repository at this point

Copy the full SHA dfd5a64View commit details -

[AsmParser] Support non-consecutive global value numbers (#80013)

llvm/llvm-project#78171 added support for non-consecutive local value numbers. This extends the support for global value numbers (for globals and functions). This means that it is now possible to delete an unnamed global definition/declaration without breaking the IR. This is a lot less common than unnamed local values, but it seems like something we should support for consistency. (Unnamed globals are used a lot in Rust though.)

Configuration menu - View commit details

-

Copy full SHA for f2df4bf - Browse repository at this point

Copy the full SHA f2df4bfView commit details -

Configuration menu - View commit details

-

Copy full SHA for 0cd8348 - Browse repository at this point

Copy the full SHA 0cd8348View commit details -

[clang][dataflow] fix assert in `Environment::getResultObjectLocation…

…` (#79608) When calling `Environment::getResultObjectLocation` with a CXXOperatorCallExpr that is a prvalue, we just hit an assert because no record was ever created. --------- Co-authored-by: martinboehme <mboehme@google.com>

Configuration menu - View commit details

-

Copy full SHA for 5c2da28 - Browse repository at this point

Copy the full SHA 5c2da28View commit details -

[Flang] Support NULL(procptr): null intrinsic that has procedure poin…

…ter argument. (#80072) This PR adds support for NULL intrinsic to have a procedure pointer argument.

Configuration menu - View commit details

-

Copy full SHA for bd8bec2 - Browse repository at this point

Copy the full SHA bd8bec2View commit details -

Configuration menu - View commit details

-

Copy full SHA for e34fd2e - Browse repository at this point

Copy the full SHA e34fd2eView commit details -

Configuration menu - View commit details

-

Copy full SHA for baf1b19 - Browse repository at this point

Copy the full SHA baf1b19View commit details -

Revert "[mlir] Lower math dialect later in gpu-lower-to-nvvm-pipeline…

… (#78556)" This reverts commit 74bf0b1. The test always fails. | mlir/test/Dialect/GPU/test-nvvm-pipeline.mlir:23:16: error: CHECK-PTX: expected string not found in input | // CHECK-PTX: __nv_expf https://lab.llvm.org/buildbot/#/builders/61/builds/53789

Configuration menu - View commit details

-

Copy full SHA for 98dbc68 - Browse repository at this point

Copy the full SHA 98dbc68View commit details -

Revert "[AArch64] Convert concat(uhadd(a,b), uhadd(c,d)) to uhadd(con…

…cat(a,c), concat(b,d))" (#80157) Reverts llvm/llvm-project#79464 while figuring out why the tests are failing.

Configuration menu - View commit details

-

Copy full SHA for 2907c63 - Browse repository at this point

Copy the full SHA 2907c63View commit details -

Configuration menu - View commit details

-

Copy full SHA for 6720e3a - Browse repository at this point

Copy the full SHA 6720e3aView commit details -

[AArch64] Use DAG->isAddLike in add_and_or_is_add (#79563)

This allows it to work with disjoint or's as well as computing the known bits.

Configuration menu - View commit details

-

Copy full SHA for d04ae1b - Browse repository at this point

Copy the full SHA d04ae1bView commit details -

[Clang][test] Add fPIC when building shared library (#80065)

Fix linking error: "ld: error: can't create dynamic relocation R_X86_64_64 against local symbol in readonly segment; recompile object files with -fPIC or pass '-Wl,-z,notext' to allow text relocations in the output"

Configuration menu - View commit details

-

Copy full SHA for b929be2 - Browse repository at this point

Copy the full SHA b929be2View commit details -

Configuration menu - View commit details

-

Copy full SHA for 16c4843 - Browse repository at this point

Copy the full SHA 16c4843View commit details -

[Exegesis] Print epsilon value in the sched model inconsistency repor…

…t (#80080) Since I've formatted the epsilon value, I don't think it's necessary to escape it.

Configuration menu - View commit details

-

Copy full SHA for 8241106 - Browse repository at this point

Copy the full SHA 8241106View commit details -

[lldb][DataFormatter][NFC] Use GetFirstValueOfLibCXXCompressedPair th…

…roughout formatters (#80133) This avoids duplicating the logic to get the first element of a libc++ `__compressed_pair`. This will be useful in supporting upcoming changes to the layout of `__compressed_pair`. Drive-by changes: * Renamed `m_item` to `size_node` for readability; `m_item` suggests it's a member variable, which it is not.

Configuration menu - View commit details

-

Copy full SHA for 08c0eb1 - Browse repository at this point

Copy the full SHA 08c0eb1View commit details -

[lldb] Add support for large watchpoints in lldb (#79962)

This patch is the next piece of work in my Large Watchpoint proposal, https://discourse.llvm.org/t/rfc-large-watchpoint-support-in-lldb/72116 This patch breaks a user's watchpoint into one or more WatchpointResources which reflect what the hardware registers can cover. This means we can watch objects larger than 8 bytes, and we can watched unaligned address ranges. On a typical 64-bit target with 4 watchpoint registers you can watch 32 bytes of memory if the start address is doubleword aligned. Additionally, if the remote stub implements AArch64 MASK style watchpoints (e.g. debugserver on Darwin), we can watch any power-of-2 size region of memory up to 2GB, aligned to that same size. I updated the Watchpoint constructor and CommandObjectWatchpoint to create a CompilerType of Array<UInt8> when the size of the watched region is greater than pointer-size and we don't have a variable type to use. For pointer-size and smaller, we can display the watched granule as an integer value; for larger-than-pointer-size we will display as an array of bytes. I have `watchpoint list` now print the WatchpointResources used to implement the watchpoint. I added a WatchpointAlgorithm class which has a top-level static method that takes an enum flag mask WatchpointHardwareFeature and a user address and size, and returns a vector of WatchpointResources covering the request. It does not take into account the number of watchpoint registers the target has, or the number still available for use. Right now there is only one algorithm, which monitors power-of-2 regions of memory. For up to pointer-size, this is what Intel hardware supports. AArch64 Byte Address Select watchpoints can watch any number of contiguous bytes in a pointer-size memory granule, that is not currently supported so if you ask to watch bytes 3-5, the algorithm will watch the entire doubleword (8 bytes). The newly default "modify" style means we will silently ignore modifications to bytes outside the watched range. I've temporarily skipped TestLargeWatchpoint.py for all targets. It was only run on Darwin when using the in-tree debugserver, which was a proxy for "debugserver supports MASK watchpoints". I'll be adding the aforementioned feature flag from the stub and enabling full mask watchpoints when a debugserver with that feature is enabled, and re-enable this test. I added a new TestUnalignedLargeWatchpoint.py which only has one test but it's a great one, watching a 22-byte range that is unaligned and requires four 8-byte watchpoints to cover. I also added a unit test, WatchpointAlgorithmsTests, which has a number of simple tests against WatchpointAlgorithms::PowerOf2Watchpoints. I think there's interesting possible different approaches to how we cover these; I note in the unit test that a user requesting a watch on address 0x12e0 of 120 bytes will be covered by two watchpoints today, a 128-bytes at 0x1280 and at 0x1300. But it could be done with a 16-byte watchpoint at 0x12e0 and a 128-byte at 0x1300, which would have fewer false positives/private stops. As we try refining this one, it's helpful to have a collection of tests to make sure things don't regress. I tested this on arm64 macOS, (genuine) x86_64 macOS, and AArch64 Ubuntu. I have not modifed the Windows process plugins yet, I might try that as a standalone patch, I'd be making the change blind, but the necessary changes (see ProcessGDBRemote::EnableWatchpoint) are pretty small so it might be obvious enough that I can change it and see what the Windows CI thinks. There isn't yet a packet (or a qSupported feature query) for the gdb remote serial protocol stub to communicate its watchpoint capabilities to lldb. I'll be doing that in a patch right after this is landed, having debugserver advertise its capability of AArch64 MASK watchpoints, and have ProcessGDBRemote add eWatchpointHardwareArmMASK to WatchpointAlgorithms so we can watch larger than 32-byte requests on Darwin. I haven't yet tackled WatchpointResource *sharing* by multiple Watchpoints. This is all part of the goal, especially when we may be watching a larger memory range than the user requested, if they then add another watchpoint next to their first request, it may be covered by the same WatchpointResource (hardware watchpoint register). Also one "read" watchpoint and one "write" watchpoint on the same memory granule need to be handled, making the WatchpointResource cover all requests. As WatchpointResources aren't shared among multiple Watchpoints yet, there's no handling of running the conditions/commands/etc on multiple Watchpoints when their shared WatchpointResource is hit. The goal beyond "large watchpoint" is to unify (much more) the Watchpoint and Breakpoint behavior and commands. I have a feeling I may be slowly chipping away at this for a while. rdar://108234227

Configuration menu - View commit details

-

Copy full SHA for 57c66b3 - Browse repository at this point

Copy the full SHA 57c66b3View commit details -

Configuration menu - View commit details

-

Copy full SHA for 35a0089 - Browse repository at this point

Copy the full SHA 35a0089View commit details -

[Libomptarget] Remove handling of old ctor / dtor entries (#80153)

Summary: A previous patch removed creating these entries in clang in favor of the backend emitting a callable kernel and having the runtime call that if present. The support for the old style was kept around in LLVM 18.0 but now that we have forked to 19.0 we should remove the support. The effect of this would be that an application linking against a newer libomptarget that still had the old constructors will no longer be called. In that case, they can either recompile or use the `libomptarget.so.18` that comes with the previous release.

Configuration menu - View commit details

-

Copy full SHA for 2542876 - Browse repository at this point

Copy the full SHA 2542876View commit details -

[libc++abi] Add temporary workaround to unblock Chrome

Chrome rolls libc++ and libc++abi as separate projects. As a result, they may not always be updated in lockstep, and this can lead to build failures when mixing libc++ that doesn't have <__thread/support.h> with libc++abi that requires it. This patch adds a workaround to make libc++abi work with both versions. While Chrome's setup is not supported, this workaround will allow them to go back to green and do the required work needed to roll libc++ and libc++abi in lockstep. This workaround will be short-lived -- I have a reminder to go back and remove it by EOW.

Configuration menu - View commit details

-

Copy full SHA for 372f7dd - Browse repository at this point

Copy the full SHA 372f7ddView commit details -

Add extra printing to TestWatchpointCount.py to debug CI fail

The way the locals are laid out on the stack on x86-64 Debian is resulting in a test failure with the new large watchpoint support. Collecting more logging before I revert/debug it.

Configuration menu - View commit details

-

Copy full SHA for dad50fe - Browse repository at this point

Copy the full SHA dad50feView commit details -

[DirectX][docs] Architecture and design philosophy of DXIL support

This documents some of the architectural direction for DXIL and tries to provide a bit of a map for where to implement different aspects of DXIL support. Pull Request: llvm/llvm-project#78221

Configuration menu - View commit details

-

Copy full SHA for 151559c - Browse repository at this point

Copy the full SHA 151559cView commit details -

[SYCL][ESIMD] Implement unified memory API for scatter(usm, ...) (int…

…el#12510) This implements the unified memory API for scatter with USM pointers. --------- Signed-off-by: Sarnie, Nick <nick.sarnie@intel.com>

Configuration menu - View commit details

-

Copy full SHA for 0bf2e66 - Browse repository at this point

Copy the full SHA 0bf2e66View commit details -

[lld] enable fixup chains by default (#79894)

Enable chained fixups in lld when all platform and version criteria are met. This is an attempt at simplifying the logic used in ld 907: https://github.com/apple-oss-distributions/ld64/blob/93d74eafc37c0558b4ffb88a8bc15c17bed44a20/src/ld/Options.cpp#L5458-L5549 Some changes were made to simplify the logic: - only enable chained fixups for macOS from 13.0 to avoid the arch check - only enable chained fixups for iphonesimulator from 16.0 to avoid the arch check - don't enable chained fixups for not specifically listed platforms - don't enable chained fixups for arm64_32

Configuration menu - View commit details

-

Copy full SHA for 775c285 - Browse repository at this point

Copy the full SHA 775c285View commit details -

Collecting more logging to debug CI bots

Watchpoint test fails on arm-ubuntu and x86-64-debian

Configuration menu - View commit details

-

Copy full SHA for cf2533e - Browse repository at this point

Copy the full SHA cf2533eView commit details -

Configuration menu - View commit details

-

Copy full SHA for 09fc333 - Browse repository at this point

Copy the full SHA 09fc333View commit details -

Add logging to WatchpointAlgorithm

When verbose lldb watch channel is enabled, print the user requested watchpoint and the resources we've broken it up into.

Configuration menu - View commit details

-

Copy full SHA for d6e1ae2 - Browse repository at this point

Copy the full SHA d6e1ae2View commit details -

[CI][NFC] Unify naming scheme for SYCL workflows. (intel#12525)

All GitHub Actions workflows added by intel/llvm project follow similar naming notation: 1. Name starts with `sycl` prefix. 2. Use dash `-` instead of underscore `_` to separate words.

Configuration menu - View commit details

-

Copy full SHA for 16a368c - Browse repository at this point

Copy the full SHA 16a368cView commit details -

Configuration menu - View commit details

-

Copy full SHA for fa42589 - Browse repository at this point

Copy the full SHA fa42589View commit details -

Revert "[CI][NFC] Unify naming scheme for SYCL workflows." (intel#12567)

Reverts intel#12525 In addition to file renaming, we need to update file names referenced inside the workflow files.

Configuration menu - View commit details

-

Copy full SHA for 1b5daa8 - Browse repository at this point

Copy the full SHA 1b5daa8View commit details -

[SYCL][ESIMD][E2E] Disable two LSC tests on DG2 (intel#12565)

They started failing in the recent driver update. I can't reproduce it locally with the same driver version but the hardware we have is a little different, maybe that's why. I made an internal tracker for this. Signed-off-by: Sarnie, Nick <nick.sarnie@intel.com>

Configuration menu - View commit details

-

Copy full SHA for 7348207 - Browse repository at this point

Copy the full SHA 7348207View commit details -

[clang-tidy] Remove cert-dcl21-cpp check (#80181)

Deprecated since clang-tidy 17. The rule DCL21-CPP has been removed from the CERT guidelines, so it does not make sense to keep the check. Fixes #42788 Co-authored-by: Carlos Gálvez <carlos.galvez@zenseact.com>

Configuration menu - View commit details

-

Copy full SHA for 4cb13f2 - Browse repository at this point

Copy the full SHA 4cb13f2View commit details -

[lldb][progress][NFC] Add unit test for progress reports (#79533)

This test is being added as a way to check the behaviour of how progress events are broadcasted when reports are started and ended with the current implementation of progress reports. Here we're mainly checking and ensuring that the current behaviour is that progress events are broadcasted individually and placed in the event queue in order of their creation and deletion.

Configuration menu - View commit details

-

Copy full SHA for 51e0d1b - Browse repository at this point

Copy the full SHA 51e0d1bView commit details -

Configuration menu - View commit details

-

Copy full SHA for c84f2ba - Browse repository at this point

Copy the full SHA c84f2baView commit details -

[flang] DEALLOCATE(pointer) should use PointerDeallocate() (#79702)

A DEALLOCATE statement on a pointer should always use PointerDeallocate() in the runtime, even if there's no STAT= or polymorphism or derived types, so that it can be checked to ensure that it is indeed a whole allocation of a pointer.

Configuration menu - View commit details

-

Copy full SHA for dc15524 - Browse repository at this point

Copy the full SHA dc15524View commit details -

[flang][runtime] Add limit check to MOD/MODULO (#80026)

When testing the arguments to see whether they are integers, check first that they are within the maximum range of a 64-bit integer; otherwise, a value of larger magnitude will set an invalid operand exception flag.

Configuration menu - View commit details

-

Copy full SHA for dbf547f - Browse repository at this point

Copy the full SHA dbf547fView commit details -

[flang][preprocessor] Replace macros in some #include directives (#80…

…039) Ensure that #include FOO undergoes macro replacement. But, as is the case with C/C++, continue to not perform macro replacement in a #include directive with <angled brackets>.

Configuration menu - View commit details

-

Copy full SHA for 6086007 - Browse repository at this point

Copy the full SHA 6086007View commit details -